# WAI-KAI CHEN Editor-in-Chief

# THE ELECTRICAL ENGINEERING HANDBOOK

https://engineersreferencebookspdf.com

# THE ELECTRICAL ENGINEERING HANDBOOK

https://engineersreferencebookspdf.com

This page intentionally left blank

# THE ELECTRICAL ENGINEERING HANDBOOK

# WAI-KAI CHEN

# EDITOR

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Academic Press is an imprint of Elsevier

https://engineersreferencebookspdf.com

Elsevier Academic Press 200 Wheeler Road, 6th Floor, Burlington, MA 01803, USA 525 B Street, Suite 1900, San Diego, California 92101-4495, USA 84 Theobald's Road, London WC1X 8RR, UK

This book is printed on acid-free paper.  $\infty$

Copyright © 2004, Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without permission in writing from the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com.uk. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Customer Support" and then "Obtaining Permissions."

#### Library of Congress Cataloging-in-Publication Data

Application submitted

# British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

ISBN: 0-12-170960-4

For all information on all Academic Press publications visit our Web site at www.books.elsevier.com

$04 \hspace{.1in} 05 \hspace{.1in} 06 \hspace{.1in} 07 \hspace{.1in} 08 \hspace{.1in} 09 \hspace{.1in} 9 \hspace{.1in} 8 \hspace{.1in} 7 \hspace{.1in} 6 \hspace{.1in} 5 \hspace{.1in} 4 \hspace{.1in} 3 \hspace{.1in} 2 \hspace{.1in} 1$

Printed in the United States of America

# Contents

|    | ntributors                                                                                                          | xiv  |

|----|---------------------------------------------------------------------------------------------------------------------|------|

|    | eface                                                                                                               | XV   |

| Ed | itor-in-Chief                                                                                                       | xvii |

| I  | <b>Circuit Theory</b><br>Krishnaiyan Thulasiraman                                                                   | 1    |

| 1  | Linear Circuit Analysis<br>P.K. Rajan and Arun Sekar                                                                | 3    |

| 2  | <b>Circuit Analysis:</b><br><b>A Graph-Theoretic Foundation</b><br><i>Krishnaiyan Thulasiraman and M.N.S. Swamy</i> | 31   |

| 3  | Computer-Aided Design                                                                                               | 43   |

| 4  | Synthesis of Networks                                                                                               | 53   |

| 5  | Nonlinear Circuits                                                                                                  | 75   |

| II | <b>Electronics</b><br><i>Krishna Shenai</i>                                                                         | 83   |

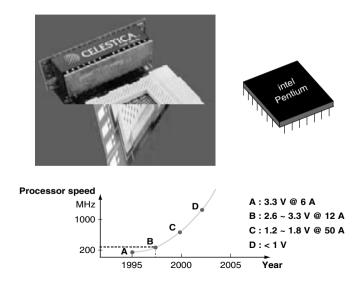

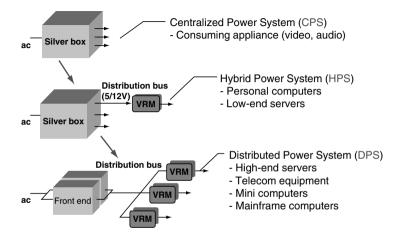

| 1  | Investigation of Power Management Issues<br>for Future Generation Microprocessors<br>Fred C. Lee and Xunwei Zhou    | 85   |

| 2  | Noise in Analog and Digital Systems                                                                                 | 101  |

| 3  | Field Effect Transistors       Operation         Veena Misra and Mehmet C. Öztürk                                   | 109  |

| 4  | Active Filters<br>Rolf Schaumann                                                                                    | 127  |

| 5  | Junction Diodes and Bipolar Junction<br>Transistors                                                                 | 139  |

| 6  | Semiconductors<br>Michael Shur                                                                                 | 153 |

|----|----------------------------------------------------------------------------------------------------------------|-----|

| 7  | <b>Power Semiconductor Devices</b><br>Maylay Trivedi and Krishna Shenai                                        | 163 |

| II | I VLSI systems<br>Magdy Bayoumi                                                                                | 177 |

| 1  | Logarithmic and Residue Number<br>Systems for VLSI Arithmetic<br>Thanos Stouraitis                             | 179 |

| 2  | Custom Memory Organization and<br>Data Transfer: Architectural Issues and<br>Exploration Methods               | 191 |

| 3  | The Role of Hardware Description<br>Languages in the Design Process of<br>Multinature Systems<br>Sorin A. Huss | 217 |

| 4  | Clock Skew Scheduling for Improved<br>Reliability<br>Ivan S. Kourtev and Eby G. Friedman                       | 231 |

| 5  | <b>Trends in Low-Power VLSI Design</b>                                                                         | 263 |

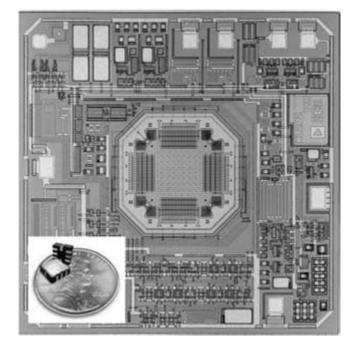

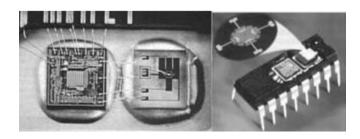

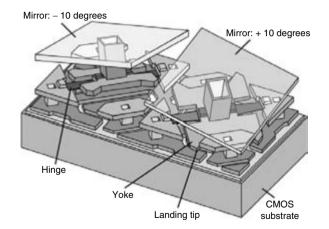

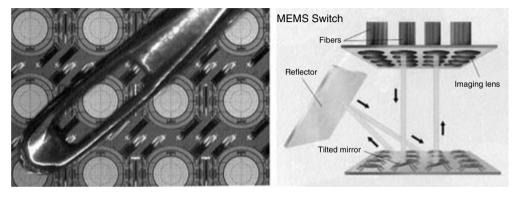

| 6  | Production and Utilization of<br>Micro Electro Mechanical Systems David J. Nagel and Mona E. Zaghloul          | 281 |

| 7  | Noise Analysis and Design in Deep<br>Submicron Technology<br>Mohamed Elgamel and Magdy Bayoumi                 | 299 |

Copyright  ${\ensuremath{\mathbb C}}$  2004 by Academic Press. All rights of reproduction in any form reserved.

vi

| 8  | Interconnect Noise Analysis and Optimization<br>in Deep Submicron Technology<br>Mohamed Elgamel and Magdy Bayoumi                       | 311 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| IV | <b>Digital Systems and Computer</b><br><b>Engineering</b><br>Sun-Yung Kung and Benjamin W. Wah                                          | 321 |

| 1  | <b>Computer Architecture.</b>                                                                                                           | 323 |

| 2  | Multiprocessors                                                                                                                         | 335 |

| 3  | <b>Configurable Computing</b><br>Wayne Luk, Peter Y. K. Cheung, and Nabeel Shirazi                                                      | 343 |

| 4  | <b>Operating Systems</b><br>Yao-Nan Lien                                                                                                | 355 |

| 5  | <b>Expert Systems</b><br><i>Yi Shang</i>                                                                                                | 367 |

| 6  | Multimedia Systems: Content-Based<br>Indexing and Retrieval<br>Faisal Bashir, Shashank Khanvilkar, Ashfaq Khokhar,<br>and Dan Schonfeld | 379 |

| 7  | <b>Multimedia Networks and Communication</b><br>Shashank Khanvilkar, Faisal Bashir,<br>Dan Schonfeld, and Ashfaq Khokhar                | 401 |

| 8  | Fault Tolerance in Computer Systems—FromCircuits to AlgorithmsShantanu Dutt, Federico Rota, Franco Trovo,and Fran Hanchek               | 427 |

| 9  | High-Level Petri Nets—Extensions,<br>Analysis, and Applications<br>Xudong He and Tadao Murata                                           | 459 |

| v  | Electromagnetics                                                                                                                        | 477 |

| 1  | Magnetostatics<br>Keith W. Whites                                                                                                       | 479 |

| 2  | Electrostatics                                                                                                                          | 499 |

| 3  | <b>Plane Wave Propagation and Reflection</b><br>David R. Jackson                                                                        | 513 |

# Contents

| 4  | Transmission LinesKrishna Naishadham                                                                                                             | 525        |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5  | <b>Guided Waves</b><br>Franco De Flaviis                                                                                                         | 539        |

| 6  | Antennas and Radiation                                                                                                                           | 553        |

|    | I Antenna Fundamentals<br>II Antenna Elements and Arrays                                                                                         | 553<br>569 |

| 7  | Microwave Passive Components<br>Ke Wu, Lei Zhu, and Ruediger Vahldieck                                                                           | 585        |

| 8  | Computational Electromagnetics: The<br>Method of Moments<br>Jian-Ming Jin and Weng Cho Chew                                                      | 619        |

| 9  | <b>Computational Electromagnetics: The Finite-<br/>Difference Time-Domain Method</b><br>Allen Taflove, Susan C. Hagness<br>and Melinda Piket-May | 629        |

| 10 | <b>Radar and Inverse Scattering</b><br><i>Hsueh-Jyh Li and Yean-Woei Kiang</i>                                                                   | 671        |

| 11 | Microwave Active Circuits and Integrated<br>Antennas<br>William R. Deal, Vesna Radisic,<br>Yongxi Qian, and Tatsuo Itoh                          | 691        |

| VI | Electric Power Systems                                                                                                                           | 707        |

| 1  | <b>Three-Phase Alternating Current Systems</b><br><i>Anjan Bose</i>                                                                              | 709        |

| 2  | <b>Electric Power System Components</b><br>Anjan Bose                                                                                            | 713        |

| 3  | Power Transformers                                                                                                                               | 715        |

| 4  | Introduction to Electric Machines                                                                                                                | 721        |

| 5  | High-Voltage Transmission                                                                                                                        | 737        |

| 6  | <b>Power Distribution.</b>                                                                                                                       | 749        |

| 7  | <b>Power System Analysis</b>                                                                                                                     | 761        |

## Contents

| 8   | <b>Power System Operation and Control</b><br>Mani Venkatasubramanian<br>and Kevin Tomsovic             | 779 |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| 9   | Fundamentals of Power SystemProtectionMladen Kezunovic                                                 | 787 |

| 10  | Electric Power QualityGerald T. Heydt                                                                  | 805 |

| VII | Signal Processing                                                                                      | 811 |

| 1   | Signals and Systems<br>Rashid Ansari and Lucia Valbonesi                                               | 813 |

| 2   | <b>Digital Filters</b><br>Marcio G. Siqueira and Paulo S.R. Diniz                                      | 839 |

| 3   | Methods, Models, and Algorithms for<br>Modern Speech Processing<br>John R. Deller, Jr. and John Hansen | 861 |

| 4   | <b>Digital Image Processing</b><br>Eduardo A.B. da Silva and Gelson V. Mendonça                        | 891 |

| 5   | <b>Multimedia Systems and Signal Processing</b><br>John R. Smith                                       | 911 |

| 6   | Statistical Signal Processing<br>Yih-Fang Huang                                                        | 921 |

| 7   | <b>VLSI Signal Processing.</b>                                                                         | 933 |

| VII | I Digital Communication and<br>Communication Networks<br>Vijay K. Garg and Yih-Chen Wang               | 949 |

| 1   | <b>Signal Types, Properties, and Processes</b><br><i>Vijay K. Garg and Yih-Chen Wang</i>               | 951 |

| 2   | <b>Digital Communication System Concepts</b><br><i>Vijay K. Garg and Yih-Chen Wang</i>                 | 957 |

| 3   | <b>Transmission of Digital Signals</b><br><i>Vijay K. Garg and Yih-Chen Wang</i>                       | 965 |

| 4   | Modulation and Demodulation<br>Technologies<br>Vijay K. Garg and Yih-Chen Wang                         | 971 |

| 5  | <b>Data Communication Concepts</b><br><i>Vijay K. Garg and Yih-Chen Wang</i>                                                          | 983  |

|----|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 6  | Communication Network<br>Architecture<br>Vijay K. Garg and Yih-Chen Wang                                                              | 989  |

| 7  | Wireless Network Access         Technologies.         Vijay K. Garg and Yih-Chen Wang                                                 | 1005 |

| 8  | Convergence of Networking<br>Technologies<br>Vijay K. Garg and Yih-Chen Wang                                                          | 1011 |

| IX | Controls and Systems                                                                                                                  | 1017 |

| 1  | Algebraic Topics in Control                                                                                                           | 1019 |

| 2  | <b>Stability</b>                                                                                                                      | 1027 |

| 3  | <b>Robust Multivariable Control</b><br>Oscar R. González and Atul G. Kelkar                                                           | 1037 |

| 4  | State Estimation                                                                                                                      | 1049 |

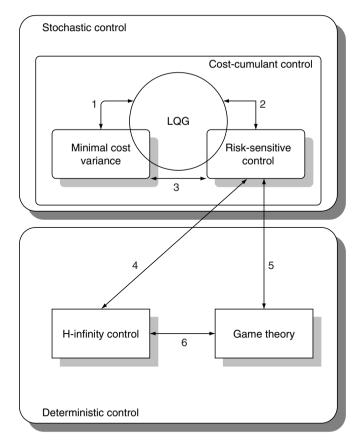

| 5  | Cost-Cumulants and Risk-Sensitive<br>Control<br>Chang-Hee Won                                                                         | 1061 |

| 6  | Frequency Domain SystemIdentificationGang Jin                                                                                         | 1069 |

| 7  | Modeling Interconnected Systems:<br>A Functional Perspective<br>Stanley R. Liberty                                                    | 1079 |

| 8  | <b>Fault-Tolerant Control</b>                                                                                                         | 1085 |

| 9  | Gain-Scheduled Controllers                                                                                                            | 1107 |

| 10 | Sliding-Mode Control Methodologies for<br>Regulating Idle Speed in Internal<br>Combustion Engines<br>Stephen Yurkovich and Xiaoqiu Li | 1115 |

- 11 Nonlinear Input/Output Control:

Volterra Synthesis

Patrick M. Sain

- 12 Intelligent Control of Nonlinear

Systems with a Time-Varying Structure ....

1139

Raúl Ordóñez and Kevin M. Passino

| 13  | <b>Direct Learning by Reinforcement</b> <i>Jennie Si</i>               | 1151 |

|-----|------------------------------------------------------------------------|------|

| 14  | Software Technologies for Complex<br>Control Systems<br>Bonnie S. Heck | 1161 |

| Ind | ex                                                                     | 1171 |

# Contributors

**Rashid Ansari** Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

Faisal Bashir

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

**Magdy Bayoumi** The Center for Advanced Computer Studies University of Louisiana at Lafayette Lafayette, Louisiana, USA

**Christopher J. Bett** Raytheon Integrated Defense Systems Tewksbury, Massachusetts, USA

**Anjan Bose** College of Engineering and Architecture Washington State University Pullman, Washington, USA

**Erik Brockmeyer** IMEC Leuven, Belgium

**Francky Catthoor** IMEC Leuven, Belgium

**Morris Chang** Department of Electrical and Computer Engineering Iowa State University Ames, Iowa, USA

**Peter Y. K. Cheung** Department of Electrical and Electronic Engineering Imperial College of Science, Technology, and Medicine London, UK

# Weng Cho Chew

Center for Computational Electromagnetics Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign Urbana, Illinois, USA

# George A. Constantinides

Department of Electrical and Electronic Engineering Imperial College of Science, Technology, and Medicine London, UK

Koen Danckaert IMEC Leuven, Belgium

**Tarek Darwish** The Center for Advanced Computer Studies University of Louisiana at Lafayette Lafeyette, Louisiana, USA

# Nirod K. Das

Department of Electrical and Computer Engineering Polytechnic University Brooklyn, New York, USA

Eduardo A.B. da Silva

Program of Electrical Engineering Federal University of Rio de Janeiro Rio de Janeiro, Brazil

William R. Deal Northrup Grumman Space Technologies Redondo Beach, California, USA

Franco De Flaviis Department of Electrical and Computer Engineering University of California at Irvine Irvine, California, USA

Copyright © 2004 by Academic Press. All rights of reproduction in any form reserved.

**Bob C. Degeneff** Department of Computer, Electrical, and Systems Engineering Rensselaer Polytechnic Institute Troy, New York, USA

John R. Deller, Jr. Department of Electrical and Computer Engineering Michigan State University East Lansing, Michigan, USA

**Rodolfo E. Diaz** Department of Electrical Engineering Ira A. Fulton School of Engineering Arizona State University Tempe, Arizona, USA

**Paulo S. R. Diniz** Program of Electrical Engineering Federal University of Rio de Janeiro Rio de Janeiro, Brazil

Shantanu Dutt Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

**Mohamed Elgamel** The Center for Advanced Computer Studies University of Louisiana at Lafayette Lafayette, Louisiana, USA

Jay Farrell Department of Electrical Engineering University of California Riverside, California, USA

**Eby G. Friedman** Department of Electrical and Computer Engineering University of Rochester Rochester, New York, USA

**Vijay K. Garg** Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

**Turan Gönen** College of Engineering and Computer Science California State University, Sacramento Sacramento, California, USA

**Oscar R. González** Department of Electrical and Computer Engineering Old Dominion University Norfolk, Virginia, USA **Ravi S. Gorur** Department of Electrical Engineering Arizona State University Tempe, Arizona, USA

**Susan C. Hagness** Department of Electrical and Computer Engineering University of Wisconsin Madison, Wisconsin, USA

**Fran Hanchek** Intel Corporation Portland, Oregan, USA

John Hansen Department of Electrical and Computer Engineering Michigan State University East Lansing, Michigan, USA

**Xudong He** School of Computer Science Florida International University Miami, Florida, USA

**Bonnie S. Heck** School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, Georgia, USA

**Gerald T. Heydt** Department of Electrical Engineering Arizona State University Tempe, Arizona, USA

**Yu-Hen Hu** Department of Electrical and Computer Engineering University of Wisconsin-Madison Madison, Wisconsin, USA

**Yih-Fang Huang** Department of Electrical Engineering University of Notre Dame Notre Dame, Indiana, USA

Sorin A. Huss Integrated Circuits and Systems Laboratory Computer Science Department Darmstadt University of Technology Darmstadt, Germany

**Tatsuo Itoh** Department of Electrical Engineering University of California, Los Angeles Los Angeles, California, USA

# Contributors

David R. Jackson Department of Electrical and Computer Engineering University of Houston Houston, Texas, USA

**Gang Jin** Ford Motor Company Dearborn, Michigan, USA

# Jian-Ming Jin

Center for Computational Electromagnetics Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign Urbana, Illinois, USA

**Atul G. Kelkar** Department of Mechanical Engineering Iowa State University Ames, Iowa, USA

**Mladen Kezunovic** Department of Electrical Engineering Texas A & M University College Station, Texas, USA

Shashank Khanvilkar Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

Ashfaq Khokhar Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

Yean-Woei Kiang Department of Electrical Engineering National Taiwan University Taipei, Taiwan

**Surin Kittitornkun** King Mongkut's Institute of Technology Ladkrabang Bangkok, Thailand

**Ivan S. Kourtev** Department of Electrical and Computer Engineering University of Pittsburgh Pittsburgh, Pennsylvania, USA

**Chidamber Kulkani** IMEC Leuven, Belgium **Sun-Yung Kung** Department of Electrical Engineering Princeton University Princeton, New Jersey, USA

**Fred C. Lee** Center for Power Electronics Systems The Bradley Department of Electrical Engineering Virginia Polytechnic Institute and State University Blacksburg, Virginia, USA

**Hsueh-Jyh Li** Department of Electrical Engineering National Taiwan University Taipei, Taiwan

Xiaoqiu Li Cummins Engine Columbus, Indiana, USA

**Stanley R. Liberty** Academic Affairs Bradley University Peoria, Illinois, USA

**Yao-Nan Lien** Department of Computer Science National Chengchi University Taipei, Taiwan

# Derong Liu

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

# Wayne Luk

Department of Electrical and Electronic Engineering Imperial College of Science, Technology, and Medicine London, UK

**Erik A. McShane** Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

**Gelson V. Mendonça** Department of Electronics COPPE/EE/Federal University of Rio de Janeiro Rio de Janeiro, Brazil

**Veena Misra** Department of Electrical and Computer Engineering North Carolina State University Raleigh, North Carolina, USA **Tadao Murata** Department of Computer Science University of Illinois at Chicago Chicago, Illinois, USA

**Lode Nachtergaele** IMEC Leuven, Belgium

**David J. Nagel** Department of Electrical and Computer Engineering The George Washington University Washington, D.C., USA

Krishna Naishadham Massachusetts Institute of Technology Lincoln Laboratory Lexington, Massachusetts, USA

**Ajoy Opal** Department of Electrical and Computer Engineering University of Waterloo Waterloo, Ontario, Canada

**Raúl Ordóñez** Department of Electrical and Computer Engineering University of Dayton Dayton, Ohio, USA

**Mehmet C. Öztürk** Department of Electrical and Computer Engineering North Carolina State University Raleigh, North Carolina, USA

**Kevin M. Passino** Department of Electrical and Computer Engineering The Ohio State University Columbus, Ohio, USA

**Melinda Piket-May** Department of Electrical and Computer Engineering University of Colorado Boulda, Colorado, USA

Yongxi Qian Department of Electrical Engineering University of California, Los Angeles Los Angeles, California, USA

**Vesna Radisic** Microsemi Corporation Los Angeles, California, USA P.K. Rajan Department of Electrical and Computer Engineering Tennessee Technological University Cookeville, Tennessee, USA

Federico Rota Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA Politecnico di Torina, Italy

Michael Sain Department of Electrical Engineering University of Notre Dame Notre Dame, Indiana, USA

**Patrick M. Sain** Raytheon Company EI Segundo, California, USA

Sheppard Joel Salon Department of Electrical Power Engineering Renssalaer Polytechnic Institute Troy, New York, USA

**Rolf Schaumann** Department of Electrical and Computer Engineering Portland State University Portland, Oregan, USA

Dan Schonfeld Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

**Cheryl B. Schrader** College of Engineering Boise State University Boise, Idaho, USA

Michael Schröter Institute for Electro Technology and Electronics Fundamentals University of Technology Dresden, Germany

Arun Sekar Department of Electrical and Computer Engineering Tennessee Technological University Cookeville, Tennessee, USA

# xii

# Contributors

# Yi Shang

Department of Computer Science University of Missouri-Columbia Columbia, Missouri, USA

## Krishna Shenai

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

Nabeel Shirazi Xilinx, Inc. San Jose, California, USA

Michael Shur Department of Electrical, Computer, and Systems Engineering Rensselaer Polytechnic Institute Troy, New York, USA

Jennie Si

Department of Electrical Engineering Arizona State University Tempe, Arizona, USA

Marcio G. Siqueira Cisco Systems Sunnyvale, California, USA

John R. Smith IBM T. J. Watson Research Center Hawthorne, New York, USA

Thanos Stouraitis Department of Electrical and Computer Engineering University of Patras Rio, Greece

**M.N.S. Swamy** Department of Electrical and Computer Engineering Concordia University Montreal, Quebec, Canada

Allen Taflove Department of Electrical and Computer Engineering Northwestern University Chicago, Illinois, USA

# Krishnaiyan Thulasiraman

School of Computer Science University of Oklahoma Norman, Oklahoma, USA Kevin Tomsovic School of Electrical Engineering and Computer Science Washington State University Pullman, Washington, USA

# Ljiljana Trajković

School of Engineering Science Simon Fraser University Vancouver, British Columbia, Canada

Malay Trivedi

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

## Franco Trovo

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA Politecnico di Torina, Italy

# **Ruediger Vahldieck**

Laboratory for Electromagnetic Fields and Microwave Electronics Swiss Federal Institute of Technology Zurich, Switzerland

Lucia Valbonesi

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

#### Arnout Vandercappelle

IMEC Leuven, Belgium

# Mani Venkatasubramanian

School of Electrical Engineering and Computer Science Washington State University Pullman, Washington, USA

# Jiri Vlach

Department of Electrical and Computer Engineering University of Waterloo Waterloo, Ontario, Canada

# Benjamin W. Wah

Computer and Systems Research Laboratory University of Illinois at Urbana-Champaign Urbana, Illinois, USA

**Yih-Chen Wang** Lucent Technologies Naperville, Illinois, USA

# Keith W. Whites

Department of Electrical and Computer Engineering South Dakota School of Mines and Technology Rapid City, South Dakota, USA

# Chang-Hee Won

Department of Electrical Engineering University of North Dakota Grand Forks, North Dakota, USA

# Ke Wu

Department of Electrical and Computer Engineering Ecole Polytechnique Montreal, Quebec, Canada

# Hung-Yu David Yang

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois, USA

# Gary G. Yen

Intelligent Systems and Control Laboratory School of Electrical and Computer Engineering Oklahoma State University Stillwater, Oklahoma, USA Stephen Yurkovich

Center for Automotive Research The Ohio State University Columbus, Ohio, USA

# Mona E. Zaghloul

Department of Electrical and Computer Engineering The George Washington University Washington, D.C., USA

# Xunwei Zhou

Center for Power Electronics Systems The Bradley Department of Electrical Engineering Virginia Polytechnic Institute and State University Blacksburg, Virginia, USA

# Lei Zhu

Department of Electrical and Computer Engineering Ecole Polytechnique Montreal, Quebec, Canada

# Purpose

The purpose of The Electrical Engineering Handbook is to provide a comprehensive reference work covering the broad spectrum of electrical engineering in a single volume. It is written and developed for the practicing electrical engineers in industry, government, and academia. The goal is to provide the most up-to-date information in classical fields of circuits, electronics, electromagnetics, electric power systems, and control systems, while covering the emerging fields of VLSI systems, digital systems, computer engineering, computeraided design and optimization techniques, signal processing, digital communications, and communication networks. This handbook is not an all-encompassing digest of everything taught within an electrical engineering curriculum. Rather, it is the engineer's first choice in looking for a solution. Therefore, full references to other sources of contributions are provided. The ideal reader is a B.S. level engineer with a need for a one-source reference to keep abreast of new techniques and procedures as well as review standard practices.

# Background

The handbook stresses fundamental theory behind professional applications. In order to do so, it is reinforced with frequent examples. Extensive development of theory and details of proofs have been omitted. The reader is assumed to have a certain degree of sophistication and experience. However, brief reviews of theories, principles, and mathematics of some subject areas are given. These reviews have been done concisely with perception. The handbook is not a textbook replacement, but rather a reinforcement and reminder of material learned as a student. Therefore, important advancement and traditional as well as innovative practices are included.

Since the majority of professional electrical engineers graduated before powerful personal computers were widely available, many computational and design methods may be new to them. Therefore, computers and software use are thoroughly covered. Not only does the handbook use traditional references to cite sources for the contributions, but it also contains *relevant* sources of information and tools that would assist the engineer in performing his/her job. This may include sources of software, databases, standards, seminars, conferences, and so forth.

# Organization

Over the years, the fundamentals of electrical engineering have evolved to include a wide range of topics and a broad range of practice. To encompass such a wide range of knowledge, the handbook focuses on the key concepts, models, and equations that enable the electrical engineer to analyze, design, and predict the behavior of electrical systems. While design formulas and tables are listed, emphasis is placed on the key concepts and theories underlying the applications.

The information is organized into nine major sections, which encompass the field of electrical engineering. Each section is divided into chapters. In all, there are 72 chapters involving 108 authors, each of which was written by leading experts in the field to enlighten and refresh knowledge of the mature engineer and educate the novice. Each section contains introductory material, leading to the appropriate applications. To help the reader, each article includes two important and useful categories: defining terms and references. *Defining terms* are key definitions and the first occurrence of each term defined is indicated in boldface in the text. The *references* provide a list of useful books and articles for following reading.

# Locating Your Topic

Numerous avenues of access to information contained in the handbook are provided. A complete table of contents is presented at the front of the book. In addition, an individual table of contents precedes each of the nine sections. The reader is urged to look over these tables of contents to become familiar with the structure, organization, and content of the book. For example, see Section VII: Signal Processing, then Chapter 7: VLSI Signal Processing, and then Chapter 7.3: Hardware Implementation. This tree-like structure enables the reader to move up the tree to locate information on the topic of interest.

The Electrical Engineering Handbook is designed to provide answers to most inquiries and direct inquirer to further sources and references. We trust that it will meet your need.

# Acknowledgments

The compilation of this book would not have been possible without the dedication and efforts of the section editors, the

publishers, and most of all the contributing authors. I particularly wish to acknowledge my wife, Shiao-Ling, for her patience and support.

> Wai-Kai Chen Editor-in-Chief

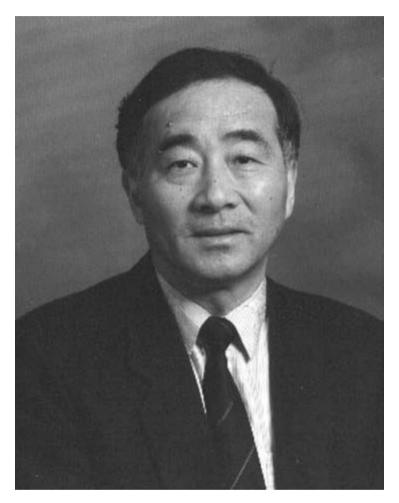

# Editor-in-Chief

**Wai-Kai Chen,** Professor and Head Emeritus of the Department of Electrical Engineering and Computer Science at the University of Illinois at Chicago. He received his B.S. and M.S. in electrical engineering at Ohio University, where he was later recognized as a Distinguished Professor. He earned his Ph.D. in electrical engineering at University of Illinois at Urbana-Champaign.

Professor Chen has extensive experience in education and industry and is very active professionally in the fields of circuits and systems. He has served as visiting professor at Purdue University, University of Hawaii at Manoa, and Chuo University in Tokyo, Japan. He was Editor-in-Chief of the *IEEE Transactions on Circuits and Systems, Series I and II*, President of the IEEE Circuits and Systems Society, and is the Founding Editor and Editor-in-Chief of the *Journal of Circuits, Systems and Computers.* He received the Lester R. Ford Award from the Mathematical Association of America,

Dr. Wai-Kai Chen

Copyright © 2004 by Academic Press. All rights of reproduction in any form reserved. the Alexander von Humboldt Award from Germany, the JSPS Fellowship Award from Japan Society for the Promotion of Science, the National Taipei University of Science and Technology Distinguished Alumnus Award, the Ohio University Alumni Medal of Merit for Distinguished Achievement in Engineering Education, the Senior University Scholar Award and the 2000 Faculty Research Award from the University of Illinois at Chicago, and the Distinguished Alumnus Award from the University of Illinois at Urbana/Champaign. He is the recipient of the Golden Jubilee Medal, the Education Award, and the Meritorious Service Award from IEEE Circuits and Systems Society, and the Third Millennium Medal from the IEEE. He has also received more than dozen honorary professorship awards from major institutions in Taiwan and China.

A fellow of the Institute of Electrical and Electronics Engineers (IEEE) and the American Association for the Advancement of Science (AAAS), Professor Chen is widely known in the profession for his *Applied Graph Theory* (North-Holland), *Theory and Design of Broadband Matching Networks* (Pergamon Press), Active Network and Feedback Amplifier Theory (McGraw-Hill), Linear Networks and Systems (Brooks/Cole), Passive and Active Filters: Theory and Implements (John Wiley), Theory of Nets: Flows in Networks (Wiley-Interscience), The Circuits and Filters Handbook (CRC Press) and The VLSI Handbook (CRC Press).

#### Dr. Wai-Kai Chen

# CIRCUIT THEORY

# Krishnaiyan Thulasiraman

School of Computer Science, University of Oklahoma, Norman, Oklahoma, USA

Circuit theory is an important and perhaps the oldest branch of electrical engineering. A circuit is an interconnection of electrical elements. These include passive elements, such as resistances, capacitances, and inductances, as well as active elements and sources (or excitations). Two variables, namely voltage and current variables, are associated with each circuit element. There are two aspects to circuit theory: **analysis and design**. Circuit analysis involves the determination of current and voltage values in different elements of the circuit, given the values of the sources or excitations. On the other hand, circuit design focuses on the design of circuits that exhibit a certain prespecified voltage or current characteristics at one or more parts of the circuit. Circuits can also be broadly classified as **linear or nonlinear circuits**.

This section consists of five chapters that provide a broad introduction to most fundamental principles and techniques in circuit analysis and design:

- Linear Circuit Analysis

- Circuit Analysis: A Graph-Theoretic Foundation

- Computer-Aided Design

- Synthesis of Networks

- Nonlinear Circuits.

This page intentionally left blank

# Linear Circuit Analysis

#### P.K. Rajan and Arun Sekar

| Department of Electrical and        |

|-------------------------------------|

| Computer Engineering,               |

| Tennessee Technological University, |

| Cookeville, Tennessee, USA          |

| 1.1  | Definitions and Terminology                                                                                                                                                   | 3  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Circuit Laws                                                                                                                                                                  | 6  |

|      | 1.2.1 Kirchhoff's Current Law • 1.2.2 Kirchhoff's Voltage Law                                                                                                                 |    |

| 1.3  | Circuit Analysis                                                                                                                                                              | 6  |

|      | 1.3.1 Loop Current Method • 1.3.2 Node Voltage Method (Nodal Analysis)                                                                                                        |    |

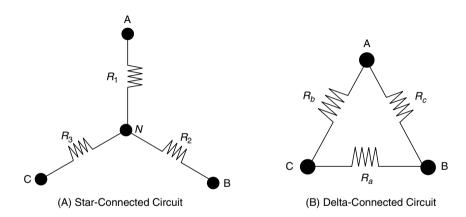

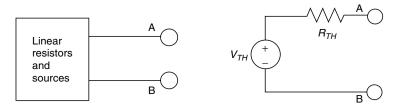

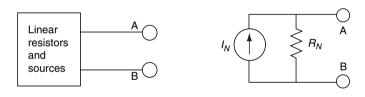

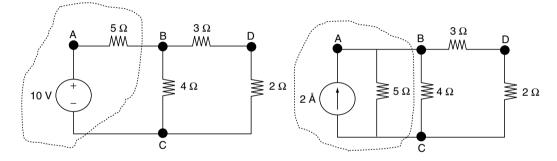

| 1.4  | Equivalent Circuits                                                                                                                                                           | 9  |

|      | 1.4.1 Series Connection • 1.4.2 Parallel Connection • 1.4.3 Star-Delta (Wye-Delta or T-Pi)                                                                                    |    |

|      | Transformation • 1.4.4 Thevenin Equivalent Circuit • 1.4.5 Norton Equivalent Circuit •                                                                                        |    |

|      | 1.4.6 Source Transformation                                                                                                                                                   |    |

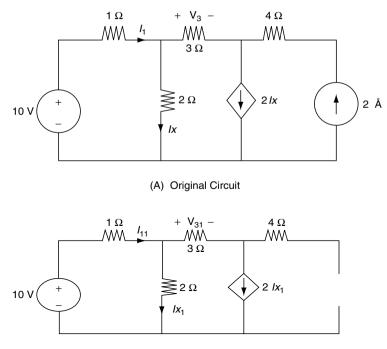

| 1.5  | Network Theorems                                                                                                                                                              | 12 |

|      | 1.5.1 Superposition Theorem • 1.5.2 Maximum Power Transfer Theorem                                                                                                            |    |

| 1.6  | Time Domain Analysis                                                                                                                                                          | 13 |

|      | 1.6.1 First-Order Circuits • 1.6.2 Second-Order Circuits • 1.6.3 Higher Order Circuits                                                                                        |    |

| 1.7  | Laplace Transform                                                                                                                                                             | 16 |

|      | 1.7.1 Definition • 1.7.2 Laplace Transforms of Common Functions • 1.7.3 Solution of                                                                                           |    |

|      | Electrical Circuits Using the Laplace Transform • 1.7.4 Network Functions                                                                                                     |    |

| 1.8  | State Variable Analysis                                                                                                                                                       | 20 |

|      | 1.8.1 State Variables for Electrical Circuits • 1.8.2 Matrix Representation of State Variable                                                                                 |    |

|      | Equations • 1.8.3 Solution of State Variable Equations                                                                                                                        |    |

| 1.9  | Alternating Current Steady State Analysis                                                                                                                                     | 22 |

|      | 1.9.1 Sinusoidal Voltages and Currents • 1.9.2 Complex Exponential Function •                                                                                                 |    |

|      | 1.9.3 Phasors in Alternating Current Circuit Analysis • 1.9.4 Phasor Diagrams •                                                                                               |    |

|      | 1.9.5 Phasor Voltage–Current Relationships of Circuit Elements • 1.9.6 Impedances and Admittances in Alternating Current Circuits • 1.9.7 Series Impedances and Parallel      |    |

|      | Admittances in Alternating Current Circuit & 1.9.7 Series Impedances and Faraner<br>Admittances • 1.9.8 Alternating Current Circuit Analysis • 1.9.9 Steps in the Analysis of |    |

|      | Phasor Circuits • 1.9.10 Methods of Alternating Current Circuit Analysis •                                                                                                    |    |

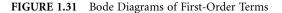

|      | 1.9.11 Frequency Response Characteristics • 1.9.12 Bode Diagrams                                                                                                              |    |

| 1.10 | Alternating Current Steady State Power                                                                                                                                        | 26 |

|      | 1.10.1 Power and Energy • 1.10.2 Power in Electrical Circuits • 1.10.3 Power Calculations                                                                                     | 10 |

|      | in AC Circuits                                                                                                                                                                |    |

# 1.1 Definitions and Terminology

An **electric charge** is a physical property of electrons and protons in the atoms of matter that gives rise to forces between atoms. The charge is measured in coulomb [C]. The charge of a proton is arbitrarily chosen as positive and has the value of  $1.601 \times 10^{-19}$  C, whereas the charge of an electron is chosen as negative with a value of  $-1.601 \times 10^{-19}$  C. Like charges repel

while unlike charges attract each other. The electric charges obey the principle of conservation (i.e., charges cannot be created or destroyed).

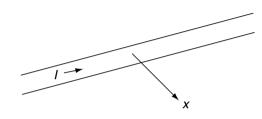

A **current** is the flow of electric charge that is measured by its flow rate as coulombs per second with the units of ampere [A]. An ampere is defined as the flow of charge at the rate of one coulomb per second (1 A = 1 C/s). In other words, current i(t) through a cross section at time *t* is given by dq/dt, where

All rights of reproduction in any form reserved.

q(t) is the charge that has flown through the cross section up to time t:

$$i(t) = \frac{dq(t)}{dt} [A].$$

(1.1)

Knowing *i*, the total charge, *Q*, transferred during the time from  $t_1$  to  $t_2$  can be calculated as:

$$Q = \int_{t_1}^{t_2} i dt \ [C].$$

(1.2)

**The voltage or potential difference**  $(V_{AB})$  between two points A and B is the amount of energy required to move a unit positive charge from B to A. If this energy is positive, that is work is done by external sources against forces on the charges, then  $V_{AB}$  is positive and point A is at a higher potential with respect to B. The voltage is measured using the unit of volt [V]. The voltage between two points is 1 V if 1 J (joule) of work is required to move 1 C of charge. If the voltage, *v*, between two points is constant, then the work, *w*, done in moving *q* coulombs of charge between the two points is given by:

$$w = vq [J]. \tag{1.3}$$

**Power** (p) is the rate of doing work or the energy flow rate. When a charge of dq coulombs is moved from point A to point B with a potential difference of v volts, the energy supplied to the charge will be v dq joule [J]. If this movement takes place in dt seconds, the power supplied to the charge will be v dq/dt watts [W]. Because dq/dt is the charge flow rate defined earlier as current *i*, the power supplied to the charge can be written as:

$$p = \nu i \ [W]. \tag{1.4}$$

The energy supplied over duration *t*1 to *t*2 is then given by:

$$w = \int_{t_1}^{t_2} vi \, dt \, [J]. \tag{1.5}$$

A **lumped electrical element** is a model of an electrical device with two or more terminals through which current can flow in or out; the flow can pass *only* through the terminals. In a twoterminal element, current flows through the element entering via one terminal and leaving via another terminal. On the other hand, the voltage is present across the element and measured between the two terminals. In a multiterminal element, current flows through one set of terminals and leaves through the remaining set of terminals. The relation between the voltage and current in an element, known as the v-*i*  relation, defines the element's characteristic. A circuit is made up of electrical elements.

**Linear elements** include a v-i relation, which can be linear if it satisfies the homogeneity property and the superposition principle. The homogeneity property refers to proportionality; that is, if *i* gives a voltage of *v*, *ki* gives a voltage of *kv* for any arbitrary constant *k*. The superposition principle implies additivity; that is, if  $i_1$  gives a voltage of  $v_1$  and  $i_2$  gives a voltage of  $v_2$ , then  $i_1 + i_2$  should give a voltage  $v_1 + v_2$ . It is easily verified that v = Ri and  $v = L \frac{di}{dt}$  are linear relations. Elements that possess such linear relations are called linear elements, and a circuit that is made up of linear elements is called a linear circuit.

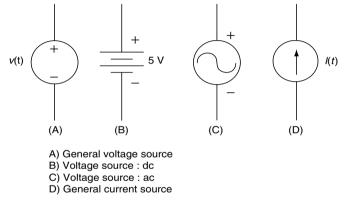

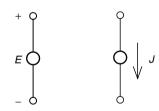

**Sources**, also known as **active elements**, are electrical elements that provide power to a circuit. There are two types of sources: (1) independent sources and (2) dependent (or controlled) sources. An independent voltage source provides a specified voltage irrespective of the elements connected to it. In a similar manner, an independent current source provides a specified current irrespective of the elements connected to it. Figure 1.1 shows representations of independent voltage and independent current sources. It may be noted that the value of an independent voltage or an independent current source may be constant in magnitude and direction (called a direct current [dc] source) or may vary as a function of time (called a time-varying source). If the variation is of sinusoidal nature, it is called an alternating current (ac) source.

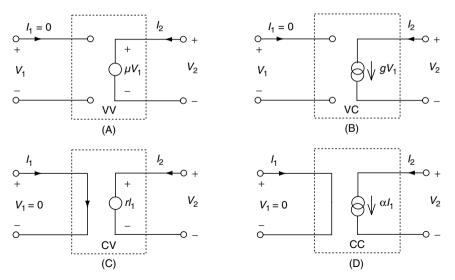

Values of dependent sources depend on the voltage or current of some other element or elements in the circuit. There are four classes of dependent sources: (1) voltagecontrolled voltage source, (2) current-controlled voltage source, (3) voltage-controlled current source and (4) currentcontrolled current source. The representations of these dependent sources are shown in Table 1.1.

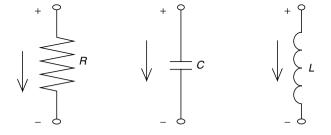

**Passive elements** consume power. Names, symbols, and the characteristics of some commonly used passive elements are given in Table 1.2. The v–i relation of a linear resistor, v = Ri,

FIGURE 1.1 Independent Voltage and Current Sources

## 1 Linear Circuit Analysis

| Element                           | Voltage and current relation                       | Representation                        |

|-----------------------------------|----------------------------------------------------|---------------------------------------|

| Voltage-controlled voltage source | $v_2 = a v_1$<br>a: Voltage gain                   | + +                                   |

|                                   |                                                    | $v_1$ $\downarrow$ $v_2$              |

|                                   |                                                    |                                       |

| Voltage-controlled current source | $i_2 = g_t v_1$<br>$g_t$ : Transfer conductance    | +                                     |

|                                   |                                                    | $v_1$ $i_2$                           |

|                                   |                                                    |                                       |

| Current-controlled voltage source | $v_2 = r_t i_1$<br><i>rt</i> : Transfer resistance | +                                     |

|                                   |                                                    | $i_1$ $\downarrow$ $\downarrow$ $v_2$ |

|                                   |                                                    |                                       |

| Current-controlled current source | $i_2 = bi_1$<br>b: Current gain                    |                                       |

|                                   |                                                    | $i_1$ $\downarrow$ $i_2$              |

|                                   |                                                    |                                       |

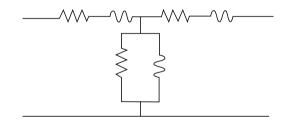

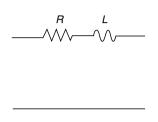

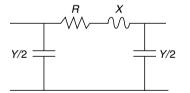

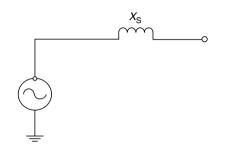

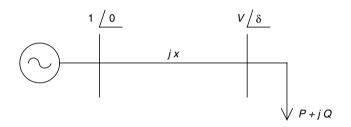

TABLE 1.2 Some Passive Elements and Their Characteristics

| Name of the element            | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The $\nu$ - <i>i</i> relation                                               | Unit      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------|

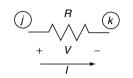

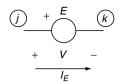

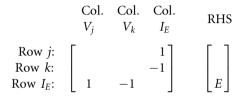

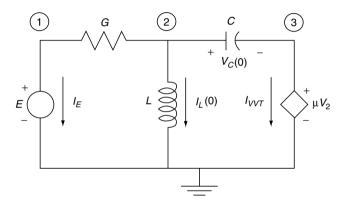

| Resistance: R                  | i $R$ $i$ $k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | v = Ri                                                                      | ohm [Ω]   |

| Inductance: L                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | v = L di/dt                                                                 | henry [H] |

| Capacitance: C                 | C $i$ $+$ $V$ $-$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i = C dv/dt                                                                 | farad [F] |

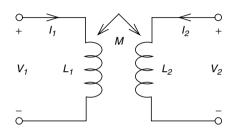

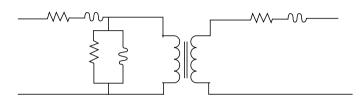

| Mutual<br>Inductance: <i>M</i> | $\begin{array}{c} + & \overbrace{L_1}^{i_1} & M & \overbrace{L_2}^{i_2} & + \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\$ | $ u_1 = M \ di_2/dt + L_1 \ di_1/dt $ $ u_2 = M \ di_1/dt + L_2 \ di_2/dt $ | henry [H] |

is known as Ohm's law, and the linear relations of other passive elements are sometimes called generalized Ohm's laws. It may be noted that in a passive element, the polarity of the voltage is such that current flows from positive to negative terminals. This polarity marking is said to follow the passive polarity convention.

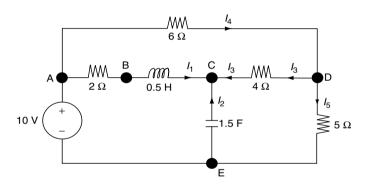

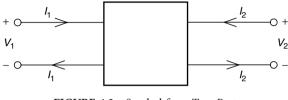

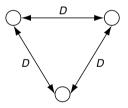

A **circuit** is formed by an interconnection of circuit elements at their terminals. A **node** is a junction point where the

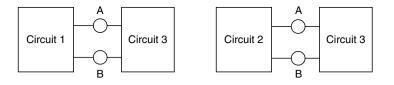

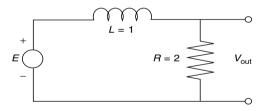

FIGURE 1.2 Example Circuit Diagram

terminals of two or more elements are joined. Figure 1.2 shows A, B, C, D, and E as nodes. A loop is a closed path in a circuit such that each node is traversed only once when tracing the loop. In Figure 1.2, ABCEA is a loop, and ABCDEA is also a loop. A **mesh** is a special class of loop that is associated with a window of a circuit drawn in a plane (planar circuit). In the same Figure ABCEA is a mesh, whereas ABCDEA is not considered a mesh for the circuit as drawn. A network is defined as a circuit that has a set of terminals available for external connections (i.e., accessible from outside of the circuit). A pair of terminals of a network to which a source, another network, or a measuring device can be connected is called a **port** of the network. A network containing such a pair of terminals is called a **one-port network**. A network containing two pairs of externally accessible terminals is called a two-port network, and multiple pairs of externally accessible terminal pairs are called a multiport network.

# 1.2 Circuit Laws

Two important laws are based on the physical properties of electric charges, and these laws form the foundation of circuit analysis. They are Kirchhoff's current law (KVL) and Kirchhoff's voltage law (KCL). While Kirchhoff's current law is based on the principle of conservation of electric charge, Kirchhoff's voltage law is based on the principle of energy conservation.

# 1.2.1 Kirchhoff's Current Law

At any instant, the algebraic sum of the currents (i) entering a node in a circuit is equal to zero. In the circuit in Figure 1.2, application of KCL at node C yields the following equation:

$$i_1 + i_2 + i_3 = 0 \tag{1.6}$$

Similarly at node D, KCL yields:

$$\dot{i}_4 - \dot{i}_3 - \dot{i}_5 = 0. \tag{1.7}$$

# 1.2.2 Kirchhoff's Voltage Law

At any instant, the algebraic sum of the voltages ( $\nu$ ) around a loop is equal to zero. In going around a loop, a useful convention is to take the voltage drop (going from positive to negative) as positive and the voltage rise (going from negative to positive) as negative. In Figure 1.2, application of KVL around the loop ABCEA gives the following equation:

$$v_{\rm AB} + v_{\rm BC} + v_{\rm CE} + v_{\rm EA} = 0.$$

(1.8)

# 1.3 Circuit Analysis

Analysis of an electrical circuit involves the determination of voltages and currents in various elements, given the element values and their interconnections. In a linear circuit, the v-irelations of the circuit elements and the equations generated by the application of KCL at the nodes and of KVL for the loops generate a sufficient number of simultaneous linear equations that can be solved for unknown voltages and currents. Various steps involved in the analysis of linear circuits are as follows:

- 1. For all the elements except the current sources, assign a current variable with arbitrary polarity. For the current sources, current values and polarity are given.

- 2. For all elements except the voltage sources, assign a voltage variable with polarities based on the passive sign convention. For voltage sources, the voltages and their polarities are known.

- 3. Write KCL equations at N 1 nodes, where N is the total number of nodes in the circuit.

- 4. Write expressions for voltage variables of passive elements using their v-i relations.

- 5. Apply KVL equations for E N + 1 independent loops, where *E* is the number of elements in the circuit. In the case of planar circuits, which can be drawn on a plane paper without edges crossing over one another, the meshes will form a set of independent loops. For nonplanar circuits, use special methods that employ topological techniques to find independent loops.

- 6. Solve the 2*E* equations to find the *E* currents and *E* voltages.

The following example illustrates the application of the steps in this analysis.

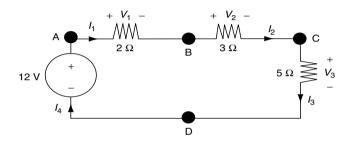

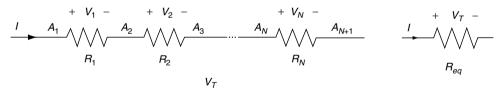

EXAMPLE 1.1. For the circuit in Figure 1.3, determine the voltages across the various elements. Following step 1, assign the currents  $I_1$ ,  $I_2$ ,  $I_3$ , and  $I_4$  to the elements. Then apply the KCL to the nodes A, B, and C to get  $I_4 - I_1 = 0$ ,  $I_1 - I_2 = 0$ , and  $I_2 - I_3 = 0$ . Solving these equations produces  $I_1 = I_2 = I_3 = I_4$ . Applying the *v*-*i* relation characteristics of the nonsource elements, you get  $V_{AB} = 2 I_1$ ,  $V_{BC} = 3 I_2$ , and  $V_{CD} = 5 I_3$ . Applying

FIGURE 1.3 Circuit for Example 1.1

the KVL to the loop ABCDA, you determine  $V_{AB} + V_{BC} + V_{CD} + V_{DA} = 0$ . Substituting for the voltages in terms of currents, you get  $2 I_1 + 3 I_1 + 5 I_1 - 12 = 0$ . Simplifying results in  $10 I_1 = 12$  to make  $I_1 = 1.2$  A. The end results are  $V_{AB} = 2.4$  V,  $V_{BC} = 3.6$  V, and  $V_{CD} = 6.0$  V.

In the above circuit analysis method, 2E equations are first set up and then solved simultaneously. For large circuits, this process can become very cumbersome. Techniques exist to reduce the number of unknowns that would be solved simultaneously. Two most commonly used methods are the loop current method and the node voltage method.

# 1.3.1 Loop Current Method

In this method, one distinct current variable is assigned to each independent loop. The element currents are then calculated in terms of the loop currents. Using the element currents and values, element voltages are calculated. After these calculations, Kirchhoff's voltage law is applied to each of the loops, and the resulting equations are solved for the loop currents. Using the loop currents, element currents and voltages are then determined. Thus, in this method, the number of simultaneous equations to be solved are equal to the number of independent loops. As noted above, it can be shown that this is equal to E - N + 1. Example 1.2 illustrates the techniques just discussed. It may be noted that in the case of planar circuits, the meshes can be chosen as the independent loops.

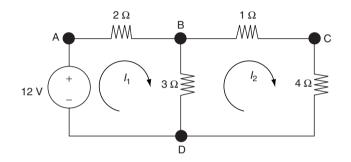

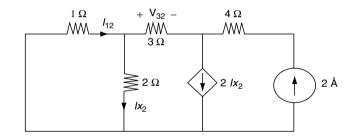

EXAMPLE 1.2. In the circuit in Figure 1.4, find the voltage across the 3- $\Omega$  resistor. First, note that there are two independent loops, which are the two meshes in the circuit, and that loop currents  $I_1$  and  $I_2$  are assigned as shown in the diagram. Then calculate the element currents as  $I_{AB} = I_1$ ,  $I_{BC} = I_2$ ,  $I_{CD} = I_2$ ,  $I_{BD} = I_1 - I_2$ , and  $I_{DA} = I_1$ . Calculate the element voltages as  $V_{AB} = 2$  $I_{AB} = 2 I_1$ ,  $V_{BC} = 1 I_{BC} = 1 I_2$ ,  $V_{CD} = 4 I_2$ , and  $V_{BD} = 3$  $I_{BD} = 3(I_1 - I_2)$ . Applying KVL to loops 1 (ABDA) and 2 (BCDB) and substituting the voltages in terms of loop currents results in:

FIGURE 1.4 Circuit for Example 1.2

$$5 I_1 - 3 I_2 = 12 -3 I_1 + 8 I_2 = 0.$$

Solving the two equations, you get  $I_1 = 96/31$  A and  $I_2 = 36/31$  A. The voltage across the 3- $\Omega$  resistor is  $3(I_1 - I_2) = 3(96/31 - 36/31) = 180/31$  A.

#### Special case 1

When one of the elements in a loop is a current source, the voltage across it cannot be written using the v-i relation of the element. In this case, the voltage across the current source should be treated as an unknown variable to be determined. If a current source is present in only one loop and is not common to more than one loop, then the current of the loop in which the current source is present should be equal to the value of the current source and hence is known. To determine the remaining currents, there is no need to write the KVL equation for the current source loop. However, to determine the voltage of the current source, a KVL equation for the current source is presented in example 1.3.

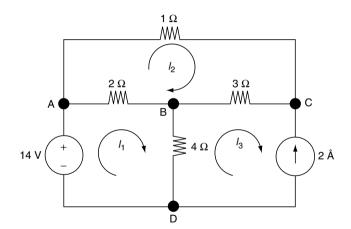

EXAMPLE 1.3. Analyze the circuit shown in Figure 1.5 to find the voltage across the current sources. The loop currents are assigned as shown. It is easily seen that  $I_3 = -2$ . Writing KVL equations for loops 1 and 2, you get:

Loop 1:  $2(I_1 - I_2) + 4(I_1 - I_3) - 14 = 0 =>$ 6  $I_1 - 2 I_2 = 6$ . Loop 2:  $I_2 + 3(I_2 - I_3) + 2(I_2 - I_1) = 0 =>$  $-2 I_1 + 6 I_2 = -6$ .

Solving the two equations simultaneously, you get  $I_1 = 3/4$  A and  $I_2 = -3/4$  A. To find the  $V_{CD}$  across the current source, write the KVL equation for the loop 3 as:

$$4(I_3 - I_1) + 3(I_3 - I_2) + V_{CD} = 0 =>$$

$V_{CD} = 4 I_1 + 3 I_2 - 7 I_3 = 14.75 V.$

FIGURE 1.5 Circuit for Example 1.3

FIGURE 1.6 Circuit for Example 1.4

# Special case 2

This case concerns a current source that is common to more than one loop. The solution to this case is illustrated in example 1.4.

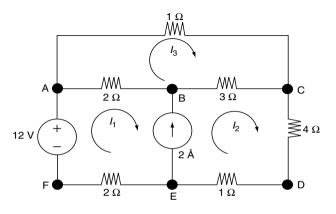

EXAMPLE 1.4. In the circuit shown in Figure 1.6, the 2 A current source is common to loops 1 and 2. One method of writing KVL equations is to treat  $V_{BE}$  as an unknown and write three KVL equations. In addition, you can write the current of the current source as  $I_2 - I_1 = 2$ , giving a fourth equation. Solving the four equations simultaneously, you determine the values of  $I_1$ ,  $I_2$ ,  $I_3$ , and  $V_{BE}$ . These equations are the following:

Loop 1:

$$2(I_1 - I_3) + V_{BE} + 2 I_1 - 12 = 0$$

=> 4  $I_1 - 2 I_3 + V_{BE} = 12$ .

Loop 2:

$$3(I_2 - I_3) + 4 I_2 + I_2 - V_{BE} = 0$$

=>  $8 I_2 - 3 I_3 - V_{BE} = 0$ .

Loop 3:

$$I_3 + 3(I_3 - I_2) + 2(I_3 - I_1) = 0$$

=> -2  $I_1 - 3 I_2 + 6 I_2 = 0$

Current source relation:  $-I_1 + I_2 = 2$ .

**FIGURE 1.7** Circuit in Figure 1.6 with the Super Loop Shown as Dotted Line

Solving the above four equations results in  $I_1 = 0.13$  A,  $I_2 = 2.13$  A,  $I_3 = 1.11$  A, and  $V_{BE} = 13.70$  V.

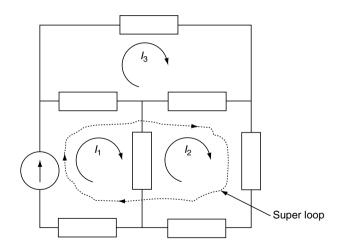

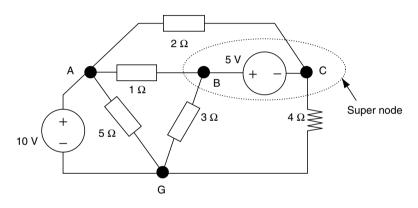

Alternative method for special case 2 (Super loop method): This method eliminates the need to add the voltage variable as an unknown. When a current source is common to loops 1 and 2, then KVL is applied on a new loop called the **super loop**. The super loop is obtained from combining loops 1 and 2 (after deleting the common elements) as shown in Figure 1.7. For the circuit considered in example 1.4, the loop ABCDEFA is the super loop obtained by combining loops 1 and 2. The KVL is applied on this super loop instead of KVL being applied for loop 1 and loop 2 separately. The following is the KVL equation for super loop ABCDEFA:

$$2(I_1 - I_3) + 3(I_2 - I_3) + 4 I_2 + I_2 + 2 I_1 - 12 = 0$$

=> 4 I\_1 + 8 I\_2 - 5 I\_3 = 12.

The KVL equation around loop 3 is written as:

$$-2 I_1 - 3 I_2 + 6 I_3 = 0.$$

The current source can be written as:

$$-I_1 + I_2 = 2.$$

Solving the above three equations simultaneously produces equations  $I_1 = 0.13$  A,  $I_2 = 2.13$  A, and  $I_3 = 1.11$  A.

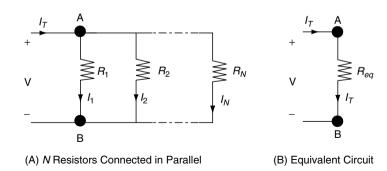

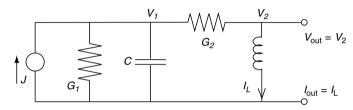

# 1.3.2 Node Voltage Method (Nodal Analysis)

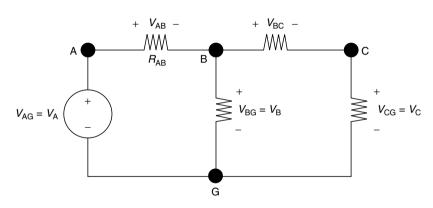

In this method, one node is chosen as the reference node whose voltage is assumed as zero, and the voltages of other nodes are expressed with respect to the reference node. For example, in Figure 1.8, the voltage of node G is chosen as the

FIGURE 1.8 Circuit with Node Voltages Marked

reference node, and then the voltage of node A is  $V_A = V_{AG}$ and that of node B is  $V_B = V_{BG}$  and so on. Then, for every element between two nodes, the element voltages may be expressed as the difference between the two node voltages. For example, the voltage of element  $R_{AB}$  is  $V_{AB} = V_A - V_B$ . Similarly  $V_{BC} = V_B - V_C$  and so on. Then the current through the element  $R_{AB}$  can be determined using the *v*-*i* characteristic of the element as  $I_{AB} = V_{AB}/R_{AB}$ . Once the currents of all elements are known in terms of node voltages, KCL is applied for each node except for the reference node, obtaining a total of *N*-1 equations where *N* is the total number of nodes.

#### Special Case 1

In branches where voltage sources are present, the v-i relation cannot be used to find the current. Instead, the current is left as an unknown. Because the voltage of the element is known, another equation can be used to solve the added unknown. When the element is a current source, the current through the element is known. There is no need to use the v-i relation. The calculation is illustrated in the following example.

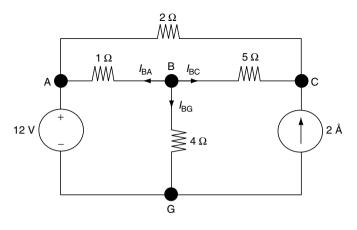

EXAMPLE 1.5. In Figure 1.9, solve for the voltages  $V_A$ ,  $V_B$ , and  $V_C$  with respect to the reference node G. At node A,  $V_A = 12$ . At node B, KCL yields:

$$I_{BA} + I_{BG} + I_{BC} = 0 =>$$